EXPLANATION:

A multiplexer or in short mux is a combinational logic circuit used to pass only one of the multiple inputs(i0,i1,i2,i3,i4,i5,i6,i7) at a time with the help of select lines(s0,s1,s2) to generate the output(y).

A 8x1(Four cross one) mux has Eight inputs and 1 output. The output of a mux will always be one. The general formulae for all types of multiplexers is, For 2n inputs, the number of selects line will be n.

For 8x1 mux when s=000, the input line i0 will be transferred to the output y; when s=001, the input line i1 will be transferred to the output y; when s=010, the input line i2 will be transferred to the output y; when s=011, the input line i3 will be transferred to the output y and so on.

Verilog code:

module mux8_1(i,s,y);

input [7:0]i;

input [2:0]s;

output reg y;

always @(i,s)

y= (~s[2])&(~s[1])&(~s[0])&i[0]|(~s[2])&(~s[1])&(s[0])&i[1]|(~s[2])&(s[1])&(~s[0])&i[2]|(~s[2])&(s[1])&(s[0])&i[3]|(s[2])&(~s[1])&(~s[0])&i[4]|(s[2])&(~s[1])&(s[0])&i[5]|(s[2])&(s[1])&(~s[0])&i[6]|(s[2])&(s[1])&(s[0])&i[7];

endmodule

Test Bench:

`timescale 1ns/1ns

module tb;

reg[7:0]i;

reg [2:0]s;

wire y;

mux8_1 DUT(i,s,y);

initial

begin

s=3'b000;i=8'b00000000;

#15 s=$random ;i=$random;

#15 s=$random ;i=$random;

#15 s=$random ;i=$random;

#15 s=$random ;i=$random;

#15 s=$random ;i=$random;

#15 s=$random ;i=$random;

#15 s=$random ;i=$random;

#15 s=$random ;i=$random;

#15 s=$random ;i=$random;

#15 s=$random ;i=$random;

#15 s=$random ;i=$random;

#15 s=$random ;i=$random;

#15 s=$random ;i=$random;

#15 s=$random ;i=$random;

#15 s=$random ;i=$random;

end

endmodule

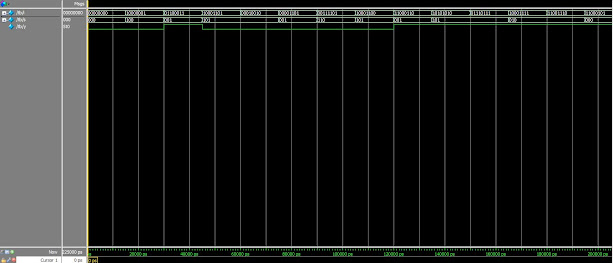

WAVEFORM:

Cheers to you all..

0 Comments

If you have any doubts , please let me know

Emoji